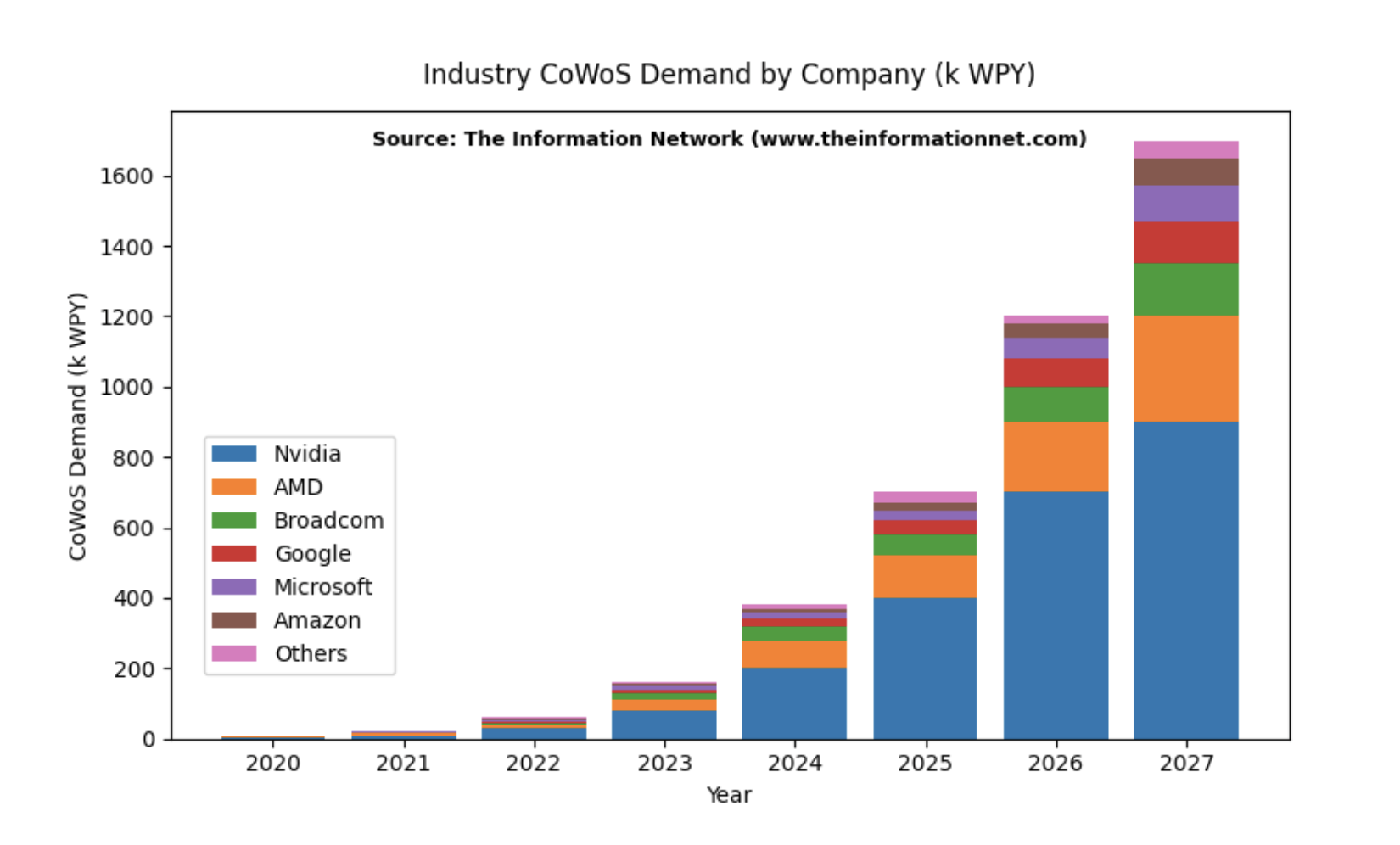

"Intel is attempting to reposition itself in the semiconductor value chain by leveraging one of the few areas where it still holds a differentiated capability-advanced packaging. The demand for CoWoS is forecasted to grow at a 64% CAGR between 2025 and 2027, driven by the rapid increase in AI accelerator complexity and the corresponding growth in HBM content per processor."

"Unlike prior semiconductor cycles driven by broad consumer demand, this growth is concentrated and constrained by packaging availability rather than wafer fabrication capacity. With Nvidia and hyperscalers consuming most available CoWoS capacity, smaller AI chip developers are forced to look for alternative packaging solutions."

Intel is repositioning itself in the semiconductor value chain by promoting its Embedded Multi-die Interconnect Bridge-T (EMIB-T) as an alternative to TSMC's CoWoS platform. The semiconductor growth is driven by hyperscaler capital expenditures linked to AI infrastructure, facing a packaging bottleneck. Demand for CoWoS is expected to grow significantly, primarily due to increased AI accelerator complexity. Major players like Nvidia and AMD dominate this demand, limiting capacity for smaller AI chip developers and creating opportunities for Intel's packaging solutions.

Read at 24/7 Wall St.

Unable to calculate read time

Collection

[

|

...

]